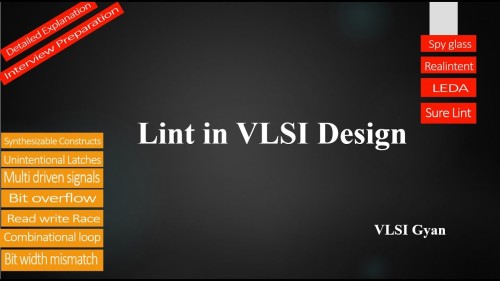

Verilog Lint essentials for RTL Design Engineer

Published 11/2024

Created by Kumar Khandagle,Gopinath Khandagle,Surekha Khandagle

MP4 | Video: h264, 1280x720 | Audio: AAC, 44.1 KHz, 2 Ch

Genre: eLearning | Language: English | Duration: 77 Lectures ( 3h 10m ) | Size: 1.11 GB

Step by Step Guide from Scratch

What you'll learn

Role of Lint in DUT analysis

Reset & Clock best practices

Naming Conventions & Assignment Operators best practices

Loop best practices

Case best practices

Function & Tasks best practices

Requirements

Fundamentals of Digital Electronics and Verilog

Description

We have two types of analysis for the DUT (Device Under Test). The first type is static analysis, where we examine the design without applying any stimulus. This involves analyzing the constructs and coding patterns to identify early bugs or applying mathematical models to check the correctness of the DUT. Examples of static analysis include linting and formal verification.The second type is dynamic analysis, where we apply a set of stimuli to the DUT based on test cases and analyze the response to verify functionality.Linting is crucial in Verilog design to ensure code quality and prevent errors. It enforces coding standards, detects bugs early, and checks for correct syntax and semantics. Using lint tools helps Verilog engineers maintain consistency across codebases, enhance readability, and preempt issues that might not affect simulation but could lead to unexpected results during synthesis.A key advantage of linting in RTL (Register Transfer Level) design is its ability to detect incorrect usage of clocks, resets, modeling styles, loops, and control structures, which can lead to unsynthesizable designs. The difficulty with these bugs is that they are often hard to identify during debugging, as they are typically logical errors. Early detection of these issues saves designers significant time and effort.

Who this course is for

Anyone interested in becoming an RTL Design Engineer.

https://rapidgator.net/file/159fc94b2f7a77150315f78dfc277e1c/Verilog_Lint_essentials_for_RTL_Design_Engineer.part2.rar.html

https://rapidgator.net/file/990e38d4e6da35f64cccc228bd8130d4/Verilog_Lint_essentials_for_RTL_Design_Engineer.part1.rar.html

https://ddownload.com/4g7jdom1ddi0/Verilog_Lint_essentials_for_RTL_Design_Engineer.part2.rar

https://ddownload.com/3cil7y1ihcn9/Verilog_Lint_essentials_for_RTL_Design_Engineer.part1.rar